MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 D Low Supply-Voltage Range: 1.8 V to 3.6 V D Ultralow Power Consumption D D D D D D D D D D D D D D D -- Active Mode: 350 A at 1 MHz, 2.2 V -- Standby Mode: 1.1 A -- Off Mode (RAM Retention): 0.2 A Five Power-Saving Modes Wake-Up From Standby Mode in Less Than 6 s 16-Bit RISC Architecture, 62.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 description The Texas Instruments MSP430 family of ultralow-power microcontrollers consists of several devices featuring different sets of peripherals targeted for various applications. The architecture, combined with five low-power modes, is optimized to achieve extended battery life in portable measurement applications.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 functional block diagram, MSP430F471x7 XIN XOUT XT2IN XT2OUT 2 2 Oscillators FLL+ DVCC1/2 DVSS1/2 AVCC AVSS P1.x/P2.x 2x8 ACLK SMCLK MCLK 16MHz CPU incl. 16 Registers Flash RAM 120kB 116kB 92kB 92kB 56kB 4kB 8kB 4kB 8kB 4kB SD16_A (w/o BUF) 7 Sigma-Delta A/D Converter P3.x/P4.x P5.x 3x8 P7.x/P8.x P9.x/P10.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 functional block diagram, MSP430F471x3 XIN XOUT XT2IN XT2OUT 2 2 Oscillators FLL+ DVCC1/2 ACLK SMCLK Flash RAM 120kB 116kB 92kB 92kB 4kB 8kB 4kB 8kB AVSS P1.x/P2.x SD16_A (w/o BUF) 3 Sigma-Delta A/D Converter P7.x/P8.x P9.x/P10.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 pin designation, MSP430F471x7IPZ 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 MSP430F471x7IPZ 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 P3.0/UCB0STE/UCA0CLK P3.1/UCB0SIMO/UCB0SDA P3.2/UCB0SOMI/UCB0SCL P3.3/UCB0CLK/UCA0STE P3.4/TA2/S39 P3.5/TB0/S38 P3.6/TB1/S37 P3.7/TB2/S36 DVSS2 XOUT XIN DVCC2 LCDCAP/R33 P5.7/R23 P5.6/LCDREF/R13 P5.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 pin designation, MSP430F471x6IPZ 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 MSP430F471x6IPZ 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 P9.4/S7 P9.3/S8 P9.2/S9 P9.1/S10 P9.0/S11 P8.7/S12 P8.6/S13 P8.5/S14 P8.4/S15 P8.3/S16 P8.2/S17 P8.1/S18 P8.0/S19 P7.7/S20 P7.6/S21 P7.5/S22 P7.4/S23 P7.3/S24 P7.2/S25 P7.1/S26 P7.0/S27 P4.7/S28 P4.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 pin designation, MSP430F471x3IPZ 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 MSP430F471x3IPZ 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 P3.0/UCB0STE/UCA0CLK P3.1/UCB0SIMO/UCB0SDA P3.2/UCB0SOMI/UCB0SCL P3.3/UCB0CLK/UCA0STE P3.4/TA2/S39 P3.5/TB0/S38 P3.6/TB1/S37 P3.7/TB2/S36 DVSS2 XOUT XIN DVCC2 LCDCAP/R33 P5.7/R23 P5.6/LCDREF/R13 P5.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Terminal Functions TERMINAL NAME NO. I/O DESCRIPTION A0.0+ 1 I SD16_A positive analog input A0.0 (see Note 1) A0.0-- 2 I SD16_A negative analog input A0.0 (see Note 1) A1.0+ 3 I SD16_A positive analog input A1.0 (see Note 1) A1.0-- 4 I SD16_A negative analog input A1.0 (see Note 1) A2.0+ 5 I SD16_A positive analog input A2.0 (see Note 1) A2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Terminal Functions (continued) TERMINAL NAME NO. I/O DESCRIPTION P8.0/S19 38 I/O General-purpose digital I/O / LCD segment output 19 P7.7/S20 39 I/O General-purpose digital I/O / LCD segment output 20 P7.6/S21 40 I/O General-purpose digital I/O / LCD segment output 21 P7.5/S22 41 I/O General-purpose digital I/O / LCD segment output 22 P7.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Terminal Functions (continued) TERMINAL NAME I/O NO. DESCRIPTION I/O DESCRIPTION P3.0/ UCB0STE/UCA0CLK 75 I/O General-purpose digital I/O / USCI_B0 slave transmit enable / USCI_A0 clock input/output P2.7/CA1 76 I/O General-purpose digital I/O / Comparator_A input P2.6/CA0 77 I/O General-purpose digital I/O / Comparator_A input P2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 short-form description CPU The MSP430 CPU has a 16-bit RISC architecture that is highly transparent to the application. All operations, other than program-flow instructions, are performed as register operations in conjunction with seven addressing modes for source operand and four addressing modes for destination operand.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 operating modes The MSP430 has one active mode and five software-selectable low-power modes of operation. An interrupt event can wake up the device from any of the five low-power modes, service the request, and restore back to the low-power mode on return from the interrupt program.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 interrupt vector addresses The interrupt vectors and the power-up starting address are located in the address range 0FFFFh to 0FFC0h. The vector contains the 16-bit address of the appropriate interrupt-handler instruction sequence. If the reset vector (at 0FFFEh) contains 0FFFFh (e.g., flash is not programmed) the CPU enters LPM4 after power-up.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 special function registers The MSP430 special function registers (SFR) are located in the lowest address space and are organized as byte mode registers. SFRs should be accessed with byte instructions. interrupt enable 1 and 2 Address 7 6 00h 4 ACCVIE rw--0 3 2 1 0 NMIIE OFIE WDTIE rw--0 rw--0 rw--0 WDTIE Watchdog timer interrupt enable. Inactive if watchdog mode is selected.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 interrupt flag register 1 and 2 Address 7 6 5 02h 4 3 2 1 0 NMIIFG RSTIFG PORIFG OFIFG WDTIFG rw--0 rw--(0) rw--(1) rw--1 rw--(0) WDTIFG Set on watchdog timer overflow or security key violation. Reset on VCC power-up or a reset condition at RST/NMI pin in reset mode. OFIFG Flag set on oscillator fault RSTIFG External reset interrupt flag.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 memory organization MSP430F47126/ MSP430F47127 MSP430F47163/ MSP430F47166/ MSP430F47167 MSP430F47173/ MSP430F47176/ MSP430F47177 MSP430F47183/ MSP430F47186/ MSP430F47187 MSP430F47193/ MSP430F47196/ MSP430F47197 Size Flash Flash 56KB 0FFFFh -- 0FFC0h 0FFFFh--002100h 92KB 0FFFFh -- 0FFC0h 018FFFh-002100h 92KB 0FFFFh -- 0FFC0h 019FFFh-003100h 116KB 0FFFFh -- 0FFC0h 01FFFFh-003100h 120

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripherals Peripherals are connected to the CPU through data, address, and control buses and can be handled using all instructions. For complete module descriptions, see the MSP430x4xx Family User’s Guide, literature number SLAU056.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 DMA controller The DMA controller allows movement of data from one memory address to another without CPU intervention. For example, the DMA controller can be used to move data from a USCI module to RAM. Using the DMA controller can increase the throughput of peripheral modules.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 universal serial communication interfaces (USCIs) (USCI_A0, USCI_B0, USCI_A1, USCI_B1) The USCI module is used for serial data communication. The USCI module supports synchronous communication protocols such as SPI (3-pin or 4-pin) and I2C and asynchronous communication protocols such as UART, enhanced UART with automatic baudrate detection (LIN), and IrDA.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Timer_B3 Timer_B3 is a 16-bit timer/counter with three capture/compare registers. Timer_B3 can support multiple capture/compares, PWM outputs, and interval timing. Timer_B3 also has extensive interrupt capabilities. Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 embedded emulation module (EEM) All MSP430F471x3, MSP430F471x6, and MSP430F471x7 devices have an EEM that supports real-time in-system debugging.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripheral file map PERIPHERALS WITH WORD ACCESS Watchdog Watchdog timer control WDTCTL 0120h Flash_A Flash control 4 Flash control 3 Flash control 2 FCTL4 FCTL3 FCTL2 01BEh 012Ch 012Ah Flash control 1 FCTL1 0128h Capture/compare register 2 TBCCR2 0196h Capture/compare register 1 TBCCR1 0194h Capture/compare register 0 TBCCR0 0192h Timer_B register TBR 0190h Capture/co

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripheral file map (continued) PERIPHERALS WITH WORD ACCESS (CONTINUED) 32-bit Hardware Multiplier Sum extend SUMEXT 013Eh Result high word RESHI 013Ch Result low word RESLO 013Ah Second operand OP2 0138h Multiply signed + accumulate/operand1 MACS 0136h Multiply + accumulate/operand1 MAC 0134h Multiply signed/operand1 MPYS 0132h Multiply unsigned/operand1 MPY 0130h

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripheral file map (continued) PERIPHERALS WITH WORD ACCESS (CONTINUED) DMA DMA Channel 0 DMA Channel 1 DMA Channel 2 24 DMA module control 0 DMACTL0 0122h DMA module control 1 DMACTL1 0124h DMA interrupt vector DMAIV 0126h DMA channel 0 control DMA0CTL 01D0h DMA channel 0 source address DMA0SA 01D2h DMA channel 0 destination address DMA0DA 01D6h DMA channel 0 transfe

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripheral file map (continued) PERIPHERALS WITH BYTE ACCESS SD16_A (see also: Peripherals with Word Access) LCD_A Channel 0 Input Control Channel 1 Input Control Channel 2 Input Control SD16INCTL0 SD16INCTL1 SD16INCTL2 0B0h 0B1h 0B2h Channel 3 Input Control Channel 4 Input Control Channel 5 Input Control Channel 6 Input Control SD16INCTL3 SD16INCTL4 SD16INCTL5 SD16INCTL6 0B3h 0B4h 0B

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripheral file map (continued) PERIPHERALS WITH BYTE ACCESS (CONTINUED) USCI_A0 USCI_A0 transmit buffer USCI_A0 receive buffer USCI_A0 status USCI_A0 modulation control USCI_A0 baud rate control 1 USCI_A0 baud rate control 0 USCI_A0 control 1 USCI_A0 control 0 USCI_A0 IrDA receive control USCI_A0 IrDA transmit control USCI_A0 auto baud rate control UCA0TXBUF UCA0RXBUF UCA0STAT UCA0MCTL UC

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripheral file map (continued) PERIPHERALS WITH BYTE ACCESS (CONTINUED) FLL+ Clock RTC (Basic Timer 1) Port P10 Port P9 Port P8 Port P7 FLL+ Control2 FLL_CTL2 055h FLL+ Control1 FLL_CTL1 054h FLL+ Control0 FLL_CTL0 053h System clock frequency control SCFQCTL 052h System clock frequency integrator SCFI1 051h System clock frequency integrator SCFI0 050h Real Time Clock

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 peripheral file map (continued) PERIPHERALS WITH BYTE ACCESS (CONTINUED) Port P5 Port P4 Port P3 Port P2 Port P1 Special p Functions 28 Port P5 resistor enable P5REN 012h Port P5 selection P5SEL 033h Port P5 direction P5DIR 032h Port P5 output P5OUT 031h Port P5 input P5IN 030h Port P4 resistor enable P4REN 011h Port P4 selection P4SEL 01Fh Port P4 direction P4DI

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 absolute maximum ratings (see Note 1) Voltage applied at VCC to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . --0.3 V to 4.1 V Voltage applied to any pin (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . --0.3 V to VCC + 0.3 V Diode current at any device terminal . . . . . . . . . . . .

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 recommended operating conditions MIN NOM MAX UNIT Supply voltage during program execution, VCC (AVCC = DVCC = VCC) (see Note 1) 1.8 3.6 V Supply voltage during program execution, SVS enabled, PORON = 1, VCC (AVCC = DVCC = VCC) (see Notes 1, 2) 2.0 3.6 V Supply voltage during program/erase flash memory, VCC (AVCC = DVCC = VCC) (see Note 1) 2.2 3.6 V --40 85 C VCC = 1.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) supply current into AVCC + DVCC excluding external current PARAMETER TEST CONDITIONS TYP MAX 2.2 V 350 400 3V 500 560 2.2 V 45 70 3V 75 110 2.2 V 11 14 3V 17 22 TA = --40C 0.7 2.0 TA = 25C 0.8 2.0 2.0 3.5 TA = 85C 5.0 9.5 TA = --40C 1.1 3.0 1.2 3.0 2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 typical characteristics -- active mode supply current (into VCC) 11.0 fDCO = 16 MHz 10.0 fDCO = 12 MHz 7.0 6.0 fDCO = 8 MHz 5.0 4.0 3.0 2.0 fDCO = 1 MHz 1.0 0.0 1.5 2.0 2.5 3.0 3.5 4.0 Active Mode Current -- mA Active Mode Current -- mA 9.0 8.0 TA = 85 C 6.0 TA = 25 C 5.0 4.0 3.0 VCC = 3 V TA = 25 C 2.0 32 POST OFFICE BOX 655303 VCC = 2.2 V 1.0 0.0 0.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) Schmitt-trigger inputs -- Ports P1 to P5, P7 to P10, RST/NMI, JTAG (TCK, TMS, TDI/TCLK, TDO/TDI) PARAMETER VIT+ VIT-- TEST CONDITIONS Positive-going P iti i input i t threshold th h ld voltage Negative-going N ti i input i t threshold th h ld voltag

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) outputs -- Ports P1 to P5, P7 to P10 PARAMETER VOH VOL High level output voltage High-level Low level output voltage Low-level VCC MIN I(OHmax) = --1.5 mA (see Note 1) TEST CONDITIONS 2.2 V VCC --0.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) typical characteristics -- outputs TYPICAL LOW-LEVEL OUTPUT CURRENT vs LOW-LEVEL OUTPUT VOLTAGE TYPICAL LOW-LEVEL OUTPUT CURRENT vs LOW-LEVEL OUTPUT VOLTAGE 50.0 VCC = 2.2 V P1.6 25.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) POR/brownout reset (BOR) (see Notes 1 and 2) PARAMETER TEST CONDITIONS VCC(start) (See Figure 8) dVCC/dt 3 V/s V(B_IT--) (See Figure 8 through Figure 10) dVCC/dt 3 V/s Vhys(B_IT--) (See Figure 8) dVCC/dt 3 V/s td(BOR) (See Figure 8) t

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) typical characteristics -- POR/brownout reset (BOR) VCC 3V VCC(drop) -- V 2 VCC = 3 V Typical Conditions 1.5 t pw 1 VCC(drop) 0.5 0 0.001 1 1000 1 ns tpw -- Pulse Width -- s 1 ns tpw -- Pulse Width -- s Figure 9.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) SVS (supply voltage supervisor/monitor) (see Note 1) PARAMETER t(SVSR) TEST CONDITIONS MIN dVCC/dt 30 V/ms (see Figure 11) 5 dVCC/dt 30 V/ms td(SVSon) SVSon, switch from VLD = 0 to VLD 0, VCC = 3 V tsettle VLD 0 (see Note 2) V(SVSstart

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 typical characteristics Software Sets VLD>0: SVS is Active VCC V(SVS_IT--) V(SVSstart) Vhys(SVS_IT--) Vhys(B_IT--) V(B_IT--) VCC(start) BrownOut Region Brownout Region Brownout 1 0 td(BOR) SVSOut 1 0 td(SVSon) Set POR 1 t d(BOR) SVS Circuit is Active From VLD > to VCC < V(B_IT--) td(SVSR) undefined 0 Figure 11.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) DCO PARAMETER MIN f(DCOCLK) f(DCO = 2) FN 8 = FN_4 FN_8 FN 4 = FN_3 FN 3 = FN_2 FN 2 = 0 0, DCOPLUS = 1 f(DCO = 27) FN 8 = FN_4 FN_8 FN 4 = FN_3 FN 3 = FN_2 FN 2 = 0 0, DCOPLUS = 1 VCC = 2.2 V/3 V FN_8 = FN_4 = FN_3 = 0, FN_2 = 1, DCOPLUS = 1 f(DCO = 2) TYP MAX 1 VCC = 2.2 V 0.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Sn - Stepsize Ratio between DCO Taps electrical characteristics over recommended operating free-air temperature (unless otherwise noted) 1.17 Max 1.11 1.07 1.06 Min 1 20 27 DCO Tap Figure 14.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) crystal oscillator, LFXT1, low-frequency mode (see Note 4) PARAMETER TEST CONDITIONS LFXT1 oscillator crystal frequency, LF mode fLFXT1,LF XTS = 0 Oscillation allowance for LF crystals OALF Integrated effective load capacitance LF mode capacitance, (see Note 1) CL,eff VCC

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) crystal oscillator, XT2 oscillator (see Note 5) PARAMETER TEST CONDITIONS VCC MIN TYP MAX UNIT fXT2,0 XT2 oscillator crystal frequency, mode 0 XT2Sx = 0 1.8 V to 3.6 V 0.4 1 MHz fXT2,1 XT2 oscillator crystal frequency, mode 1 XT2Sx = 1 1.8 V to 3.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) typical characteristics -- XT2 oscillator Oscillation Allowance -- Ohms 100000.00 10000.00 1000.00 XT2Sx = 2 100.00 XT2Sx = 0 10.00 0.10 1.00 XT2Sx = 1 10.00 100.00 Crystal Frequency -- MHz Figure 16.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) wake-up LPM3 PARAMETER TEST CONDITIONS VCC MIN f = 1 MHz td(LPM3) UNIT 6 f = 2 MHz Delay time MAX 6 2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) Comparator_A (see Note 1) PARAMETER TEST CONDITIONS I(CC) CAON = 1, 1 CARSEL = 0 0, CAREF = 0 I(Refladder/RefDiode) CAON = 1, CARSEL = 0, CAREF = 1/2/3, No load at P2.6/CA0 and P2.7/CA1 V(Ref025) V(Ref050) Voltage @ 0.25 V V CC Voltage @ 0.5 V V MIN TYP MAX 2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) typical characteristics REFERENCE VOLTAGE vs FREE-AIR TEMPERATURE REFERENCE VOLTAGE vs FREE-AIR TEMPERATURE 650 650 VCC = 2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) Timer_A PARAMETER TEST CONDITIONS fTA Timer A clock frequency Timer_A Internal: SMCLK, ACLK, External: TACLK, TACLK INCLK INCLK, Duty cycle = 50% 10% tTA,cap Timer_A, capture timing TA0, TA1, TA2 VCC MIN MAX 2.2 V 10 3V 16 2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) USCI (UART mode) -- recommended operating conditions PARAMETER fUSCI USCI input clock frequency fBITCLK BITCLK clock frequency (equals baud rate in MBaud) CONDITIONS MIN Internal: SMCLK, ACLK External: UCLK Duty cycle = 50% 10% MAX UNIT fSYST

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) 1/fUCxCLK CKPL=0 UCLK CKPL=1 tLO/HI tLO/HI tSU,MI tHD,MI SOMI tHD,MO tVALID,MO SIMO Figure 21. SPI Master Mode, CKPH = 0 1/fUCxCLK CKPL=0 UCLK CKPL=1 tLO/HI tLO/HI tHD,MI tSU,MI SOMI tHD,MO tVALID,MO SIMO Figure 22.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) USCI (SPI slave mode) (see Note 1, Figure 23, and Figure 24) PARAMETER TEST CONDITIONS VCC MIN TYP MAX UNIT tSTE,LEAD STE lead time STE low to clock 2.2 V/3 V tSTE,LAG STE lag time Last clock to STE high 2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) tSTE,LEAD tSTE,LAG STE 1/fUCxCLK CKPL=0 UCLK CKPL=1 tLO/HI tLO/HI tSU,SI tHD,SI SIMO tHD,SO tSTE,ACC tVALID,SO tSTE,DIS SOMI Figure 23.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) USCI (I2C mode) (see Figure 25) PARAMETER fUSCI USCI input clock frequency fSCL SCL clock frequency TEST CONDITIONS VCC MIN TYP Internal: SMCLK, ACLK External: UCLK Duty cycle = 50% 10% MAX UNIT fSYSTEM MHz 400 kHz 2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) SD16_A, power supply and recommended operating conditions PARAMETER AVCC ISD16 fSD16 TEST CONDITIONS VCC MIN AVCC = DVCC AVSS = DVSS = 0V Analog supply voltage Analog supply s ppl current: c rrent 1 acti active e SD16 A channel including SD16_A internal reference Analog fr

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) SD16_A, performance (fSD16 = 1 MHz, SD16OSRx = 256, SD16REFON = 1) PARAMETER SINAD G TEST CONDITIONS EOS Offset error dEOS/dT Offset error temperature coefficient CMRR Common mode rejection Common-mode ratio MIN TYP MAX SD16GAINx = 1, Signal amplitude VPP = 500 mV 3V

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) typical characteristics -- SD16_A SINAD performance over OSR 100.0 95.0 90.0 SINAD -- dB 85.0 80.0 75.0 70.0 65.0 60.0 55.0 50.0 10.00 100.00 1000.00 OSR Figure 26.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued) SD16_A, built-in voltage reference PARAMETER TEST CONDITIONS VCC VREF Internal reference voltage SD16REFON = 1, SD16VMIDON = 0 3V IREF Reference supply current SD16REFON = 1, SD16VMIDON = 0 3V TC Temperature coefficient SD16REFON = 1, SD16VMIDON = 0 (see Note 1) 3V C

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) flash memory PARAMETER VCC(PGM/ ERASE) TEST CONDITIONS VCC Program and erase supply voltage MIN TYP 2.2 fFTG Flash timing generator frequency IPGM Supply current from VCC during program 2.2 V/3.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 APPLICATION INFORMATION input/output schematics Port P1, P1.0 to P1.5, input/output with Schmitt trigger DVSS P1REN.x P1DIR.x 0 P1OUT.x 0 1 0 DVCC 1 Bus Keeper P1SEL.x EN P1IN.x EN Module X IN 1 Direction 0: Input 1: Output 1 Module X OUT DVSS P1.0/TA0 P1.1/TA0/MCLK P1.2/TA1 P1.3/TBOUTH/SVSOUT P1.4/TBCLK/SMCLK P1.5/TACLK/ACLK D P1IE.x P1IRQ.x EN Q P1IFG.x P1SEL.x P1IES.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P1 (P1.0 to P1.5) pin functions PIN NAME (P1.X) (P1 X) P1.0/TA0 / X 0 FUNCTION P1.0 (I/O) Timer_A3.CCI0A Timer_A3.TA0 P1.1/TA0/MCLK / / P1.2/TA1 / P1.3// TBOUTH/SVSOUT P1.4/TBCLK/SMCLK / / P1.5/TACLK/ACLK / / 1 2 3 4 5 P1DIR.x P1SEL.x I: 0, O: 1 0 0 1 1 1 I: 0, O: 1 0 Timer_A3.CCI0B 0 1 MCLK 1 1 I: 0, O: 1 0 Timer_A3.CCI1A 0 1 Timer_A3.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P1, P1.6 and P1.7, input/output with Schmitt trigger DVSS P1REN.x P1DIR.x USCI Direction Control 0 P1OUT.x 0 Module X OUT 1 DVSS 0 DVCC 1 1 Direction 0: Input 1: Output 1 Bus Keeper P1SEL.x P1.6/UCA1TXD/UCA1SIMO P1.7/UCA1RXD/UCA1SOMI EN P1IN.x EN Module X IN D P1IE.x P1IRQ.x EN Q P1IFG.x P1SEL.x P1IES.x Set Interrupt Edge Select Port P1 (P1.6 and P1.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P2, P2.0 to P2.5, input/output with Schmitt trigger CAPD.x P2REN.x P2DIR.x USCI Direction Control 0 P2OUT.x 0 Module X OUT 1 DVSS 0 DVCC 1 Direction 0: Input 1: Output 1 Bus Keeper P2SEL.x EN P2IN.x EN Module X IN D P2IE.x P2IRQ.x EN Q P2IFG.x P2SEL.x P2IES.x 62 1 Set Interrupt Edge Select POST OFFICE BOX 655303 DALLAS, TEXAS 75265 P2.0/UCB1STE/UCA1CLK P2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P2 (P2.0 to P2.5) pin functions PIN NAME (P2.X) (P2 X) X P2.0// UCB1STE/UCA1CLK 4 P2.1// UCB1SIMO/UCB1SDA 4 CONTROL BITS / SIGNALS FUNCTION P2.0 (I/O) UCB1STE/UCA1CLK (see Note 1, 2, 3) Input buffer disabled (see Note 6) P2.2// UCB1SOMI/UCB1SCL P2.3// UCB1CLK/UCA1STE P2.4// UCA0TXD/UCA0SIMO P2.5// UCA0RXD/UCA0SOMI 4 4 4 5 P2.1 (I/O) P2DIR.x P2SEL.x CAPD.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P2, P2.6 and P2.7, input/output with Schmitt trigger Pad Logic To Comparator_A From Comparator_A (internal signal) CAPD.x P2REN.x P2DIR.x 0 0 Module X OUT 1 0 1 1 Direction 0: Input 1: Output 1 P2OUT.x DVSS DVCC P2.6/CA0 P2.7/CA1 Bus Keeper P2SEL.x EN P2IN.x EN Module X IN D P2IE.x P2IRQ.x EN Q P2IFG.x Set Interrupt Edge Select P2SEL.x P2IES.x Port P2 (P2.6 and P2.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P3, P3.0 to P3.3, input/output with Schmitt trigger Pad Logic DVSS P3REN.x P3DIR.x USCI Direction Control 0 P3OUT.x 0 Module X OUT 1 DVSS 0 DVCC 1 1 Direction 0: Input 1: Output 1 Bus Keeper P3SEL.x P3.0/UCB0STE/UCA0CLK P3.1/UCB0SIMO/UCB0SDA P3.2/UCB0SOMI/UCB0SCL P3.3/UCB0CLK/UCA0STE EN P3IN.x EN Module X IN D Port P3 (P3.0 to P3.3) pin functions PIN NAME (P3.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P3, P3.4, input/output with Schmitt trigger Pad Logic Segment S39 LCDS36 P3REN.4 P3DIR.4 0 0 Module X OUT 1 0 1 1 Direction 0: Input 1: Output 1 P3OUT.4 DVSS DVCC P3.4/TA2/S39 Bus Keeper P3SEL.4 EN P3IN.4 EN Module X IN D Port P3 (P3.4) pin functions PIN NAME (P3.X) (P3 X) P3.4/TA2/S39 / / X 4 FUNCTION P3SEL.x LCDS36 I: 0, O: 1 0 0 Timer_A3.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P3, P3.5 to P3.7, input/output with Schmitt trigger Timer_B Output Tristate Logic P1.3/TBOUTH/SVSOUT P1SEL.3 P1DIR.3 Pad Logic Segment Sz LCDS36 P3REN.x P3DIR.x 0 0 Module X OUT 1 0 1 1 Direction 0: Input 1: Output 1 P3OUT.x DVSS DVCC Bus Keeper P3SEL.x P3.5/TB0/S38 P3.6/TB1/S37 P3.7/TB2/S36 EN P3IN.x EN Module X IN D Port P3 (P3.5 to P3.7) pin functions PIN NAME (P3.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P4, P4.0 and P4.1, input/output with Schmitt trigger Pad Logic Segment Sz LCDS32 P4REN.x P4DIR.x 0 0 Module X OUT 1 0 1 1 Direction 0: Input 1: Output 1 P4OUT.x DVSS DVCC P4.0/CAOUT/S35 P4.1/DMAE0/S34 Bus Keeper P4SEL.x EN P4IN.x EN Module X IN D Port P4 (P4.0 and P4.1) pin functions PIN NAME (P4.X) (P4 X) P4.0/CAOUT/S35 / / P4.1/DMAE0/S34 / / X 0 1 FUNCTION P4DIR.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P4, P4.2 to P4.7, input/output with Schmitt trigger Pad Logic Segment Sz LCDS... P4REN.x P4DIR.x 0 0 Module X OUT 1 0 1 Bus Keeper P4SEL.x EN P4IN.x EN Module X IN 1 Direction 0: Input 1: Output 1 P4OUT.x DVSS DVCC P4.2/S33 P4.3/S32 P4.4/S31 P4.5/S30 P4.6/S29 P4.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P4 (P4.2 and P4.3) pin functions PIN NAME (P4.X) (P4 X) P4.2/S33 / X 2 CONTROL BITS / SIGNALS FUNCTION P4.2 (I/O) N/A P4.3/S32 / 3 P4DIR.x P4SEL.x LCDS32 I: 0, O: 1 0 0 0 1 0 DVSS 1 1 0 S33 X X 1 P4.3 (I/O) I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 S32 X X 1 NOTES: 1. X: Don’t care 2. N/A: Not available or not applicable. Port P4 (P4.4 to P4.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P5, P5.0, input/output with Schmitt trigger Pad Logic To SVS SVSCTL.VLDx=15 P5REN.0 P5DIR.0 0 1 P5OUT.0 0 DVSS 1 DVSS 0 DVCC 1 1 Direction 0: Input 1: Output P5.0/SVSIN Bus Keeper P5SEL.0 EN P5IN.0 Port P5 (P5.0) pin functions PIN NAME (P5.X) (P5 X) P5.0/SVSIN / X 0 FUNCTION P5.0 (I/O) (see Note 1) SVSIN (see Notes 1 and 3) CONTROL BITS / SIGNALS P5DIR.x P5SEL.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P5, P5.1 to P5.7, input/output with Schmitt trigger Pad Logic LCD Signal P5REN.x P5DIR.x 0 0 DVSS 1 0 1 1 Direction 0: Input 1: Output 1 P5OUT.x DVSS DVCC Bus Keeper P5SEL.x EN P5IN.x P5.1/COM0 P5.2/COM1 P5.3/COM2 P5.4/COM3 P5.5/R03 P5.6/LCDREF/R13 P5.7/R23 Port P5 (P5.1 to P5.7) pin functions PIN NAME (P5 (P5.X) X) X P5.1/COM0 2 P5.2/COM1 / 2 FUNCTION P5.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P7 to port P10, input/output with Schmitt trigger Pad Logic Segment Sz LCDS... PyREN.x PyDIR.x 0 0 Module X OUT 1 0 1 1 Direction 0: Input 1: Output 1 PyOUT.x DVSS DVCC Py.x/Sz Bus Keeper PySEL.x EN PyIN.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P7 (P7.0 to P7.3) pin functions PIN NAME (P7.X) (P7 X) P7.0/S27 / X 0 CONTROL BITS / SIGNALS FUNCTION P7.0 (I/O) N/A P7.1/S26 / 1 2 3 LCDS24 0 0 0 1 0 1 1 0 S27 X X 1 P7.1 (I/O) I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 P7.2 (I/O) N/A P7.3/S24 / P7SEL.x DVSS S26 P7.2/S25 / P7DIR.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P8 (P8.0 to P8.3) pin functions PIN NAME (P8.X) (P8 X) P8.0/S19 P8.1/S18 X 0 1 CONTROL BITS / SIGNALS FUNCTION P8DIR.x P8SEL.x LCDS16 I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 S19 X X 1 P8.0 (I/O) P8.0 (I/O) I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 S18 P8.2/S17 P8.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P9 (P9.0 to P9.3) pin functions PIN NAME (P9.X) (P9 X) P9.0/S11 P9.1/S10 X 0 1 CONTROL BITS / SIGNALS FUNCTION P9DIR.x P9SEL.x LCDS8 I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 S11 X X 1 P9.0 (I/O) P9.1 (I/O) I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 S10 P9.2/S9 P9.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Port P10 (P10.0 to P10.3) pin functions PIN NAME (P10.X) (P10 X) P10.0/S3 P10.1/S2 X 0 1 CONTROL BITS / SIGNALS FUNCTION P10DIR.x P10SEL.x LCDS0 I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 S3 X X 1 P10.0 (I/O) P10.1 (I/O) I: 0, O: 1 0 0 N/A 0 1 0 DVSS 1 1 0 S2 P10.2/S1 P10.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 JTAG pins (TMS, TCK, TDI/TCLK, TDO/TDI), input/output with Schmitt trigger or output TDO Controlled by JTAG Controlled by JTAG TDO/TDI JTAG Controlled by JTAG DVCC TDI Burn and Test Fuse TDI/TCLK Test and Emulation DVCC TMS Module TMS DVCC TCK TCK RST/NMI Tau ~ 50 ns Brownout TCK 78 POST OFFICE BOX 655303 DALLAS, TEXAS 75265 G D U S G D U S

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 JTAG fuse check mode MSP430 devices that have the fuse on the TDI/TCLK terminal have a fuse check mode that tests the continuity of the fuse the first time the JTAG port is accessed after a power-on reset (POR). When activated, a fuse check current (I(TF)) of 1 mA at 3 V can flow from the TDI/TCLK pin to ground if the fuse is not burned.

MSP430F471x3, MSP430F471x6, MSP430F471x7 MIXED SIGNAL MICROCONTROLLER SLAS626C -- OCTOBER 2008 -- REVISED MARCH 2011 Data Sheet Revision History LITERATURE NUMBER SUMMARY SLAS626 Product Preview release SLAS626A Production Data release SLAS626B Added MSP430F471x3, MSP430F47126, and MSP430F47127 devices SLAS626C Corrected pin numbers in BSL function table (page 16) Changed limits on td(SVSon) parameter (page 38) NOTE: Page and figure numbers refer to the respective document revision and may differ

PACKAGE OPTION ADDENDUM www.ti.

PACKAGE OPTION ADDENDUM www.ti.

PACKAGE OPTION ADDENDUM www.ti.com 11-Apr-2013 Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material) (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) Multiple Top-Side Markings will be inside parentheses.

PACKAGE MATERIALS INFORMATION www.ti.com 10-Nov-2012 TAPE AND REEL INFORMATION *All dimensions are nominal Device Package Package Pins Type Drawing SPQ Reel Reel A0 Diameter Width (mm) (mm) W1 (mm) B0 (mm) K0 (mm) P1 (mm) W Pin1 (mm) Quadrant MSP430F47163IPZR LQFP PZ 100 1000 330.0 24.4 17.0 17.0 2.1 20.0 24.0 Q2 MSP430F47173IPZR LQFP PZ 100 1000 330.0 24.4 17.0 17.0 2.1 20.0 24.0 Q2 MSP430F47183IPZR LQFP PZ 100 1000 330.0 24.4 17.0 17.0 2.1 20.0 24.

PACKAGE MATERIALS INFORMATION www.ti.com 10-Nov-2012 *All dimensions are nominal Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm) MSP430F47163IPZR LQFP PZ 100 1000 367.0 367.0 45.0 MSP430F47173IPZR LQFP PZ 100 1000 367.0 367.0 45.0 MSP430F47183IPZR LQFP PZ 100 1000 367.0 367.0 45.0 MSP430F47193IPZR LQFP PZ 100 1000 367.0 367.0 45.

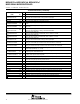

MECHANICAL DATA MTQF013A – OCTOBER 1994 – REVISED DECEMBER 1996 PZ (S-PQFP-G100) PLASTIC QUAD FLATPACK 0,27 0,17 0,50 75 0,08 M 51 76 50 100 26 1 0,13 NOM 25 12,00 TYP Gage Plane 14,20 SQ 13,80 16,20 SQ 15,80 0,05 MIN 1,45 1,35 0,25 0°– 7° 0,75 0,45 Seating Plane 0,08 1,60 MAX 4040149 /B 11/96 NOTES: A. All linear dimensions are in millimeters. B. This drawing is subject to change without notice. C.

IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.