Datasheet

I2C

CLK1

CLK

0

Bit 0 to Bit 20

DS92LX2121, DS92LX2122

SNLS330I –MAY 2010–REVISED APRIL 2013

www.ti.com

FUNCTIONAL DESCRIPTION

The DS92LX2121 / DS92LX2122 Channel Link III chipset is intended for camera applications. The Serializer/

Deserializer chipset operates from a 10 MHz to 50 MHz pixel clock frequency. The DS92LX2121 transforms a

21-bit wide parallel LVCMOS data bus along with a bi-directional back channel control bus into a single high-

speed differential pair. The high speed serial bit stream contains an embedded clock and DC-balance information

which enhances signal quality to support AC coupling. The DS92LX2122 receives the single serial data stream

and converts it back into a 21-bit wide parallel data bus together with the back channel data bus.

The control channel function of the DS92LX2121 / DS92LX2122 provides bi-directional communication between

the image sensor and Electronic Control Unit (ECU). The integrated back channel transfers data bi-directionally

over the same differential pair used for video data interface. This interface offers advantages over other chipsets

by eliminating the need for additional wires for programming and control. The back channel bus is controlled via

an I

2

C port. The bi-directional back channel offers asymmetrical communication and is not dependent on video

blanking intervals.

DISPLAY APPLICATION

The DS92LX2121 / DS92LX2122 chipset is intended for interface between a host (graphics processor, FPGA,

etc.) and a Display. It supports a 21 bit parallel video bus for 18-bit color depth (RGB666) display format. In a

RGB666 configuration, 18 color bits (R [5:0], G[5:0], B[5:0]), Pixel Clock (PCLK) and three control bits (VS, HS

and DE) are supported across the serial link. The DS92LX2121 Serializer accepts a 21-bit parallel data bus

along with a bi-directional control bus. The parallel data and bi-directional control channel information is

converted into a single differential link. The integrated bi-directional control channel bus supports I

2

C compatible

operation for controlling auxiliary data transport to and from host processor and display module. The

DS92LX2122 Deserializer extracts the clock/control information from the incoming data stream and reconstructs

the 21-bit data with control channel data.

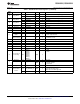

SERIAL FRAME FORMAT

The DS92LX2121 / DS92LX2122 chipset will transmit and receive a pixel of data in the following format:

Figure 23. Serial Bitstream for 28-bit Symbol

The High Speed Forward Channel is a 28-bit symbol composed of 21 bits of data containing video data & control

information transmitted from Serializer to Deserializer. CLK1 and CLK0 represent the embedded clock in the

serial stream. CLK1 is always HIGH and CLK0 is always LOW. This data payload is optimized for signal

transmission over an AC coupled link. Data is randomized, balanced and scrambled.

The bi-directional control channel data is transferred along with the high-speed forward data over the same serial

link. This architecture provides a full duplex low speed forward channel across the serial link together with a high

speed forward channel without the dependence of the video blanking phase.

DESCRIPTION OF BI-DIRECTIONAL CONTROL BUS AND I

2

C MODES

The I

2

C compatible interface allows programming of the DS92LX2121, DS92LX2122, or an external remote

device (such as a display) through the bi-directional control channel. Register programming transactions to/from

the DS92LX2121 / DS92LX2122 chipset are employed through the clock (SCL) and data (SDA) lines. These two

signals have open drain I/Os and both lines must be pulled-up to V

DDIO

by external resistor. Figure 5 shows the

timing relationships of the clock (SCL) and data (SDA) signals. Pull-up resistors or current sources are required

on the SCL and SDA busses to pull them high when they are not being driven low. A logic zero is transmitted by

driving the output low. A logic high is transmitted by releasing the output and allowing it to be pulled-up

externally. The appropriate pull-up resistor values will depend upon the total bus capacitance and operating

speed. The DS92LX2121 / DS92LX2122 I

2

C bus data rate supports up to 100 kbps according to I2C

specification.

22 Submit Documentation Feedback Copyright © 2010–2013, Texas Instruments Incorporated

Product Folder Links: DS92LX2121 DS92LX2122