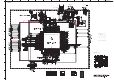

Service manual

IC800

CB801

IC802 IC801

CB802

A

1

2

3

4

5

6

7

8

9

10

BCDEFGH I JK

L MN

DVR-700/NS-PSW700/NS-P700

104

MAIN 4/4

1.7

1.8

3.4

0.9

0.9

0

1.8

5.0

5.0

3.4

0

0

1.1

1.9

5.0

5.1

5.1

1.7

0

0

1.7

1.7

3.3

3.3

1.9

0

0

1.3

0.7

1.7

0

0

0

12.0

12.0

26.3

4.3

00

30.3

15.1

15.1

30.3

30.3

15.1

26.3

11.6

0

0

30.3

0

0

0

0

3.3

3.3

3.3

0

0

0

0

0

0

12.0

12.0

12.0

12.0

26.3

12.0

4.3

3.3

4.3

1.7

0

0

30.3

30.3

30.3

15.1

15.1

30.3

0

11.4

12.0

30.3

0

0

26.3

11.6

15.1

15.1

0

0

30.3

0

0

0

0

0

0

0

3.3

0

0

0

12.0

12.0

1.7

3.3

3.3

0

30.3

30.3

10.3

0

0

11.4

4.3

1.7

3.3

SW

L/R

OUT L

OUT SW

to MAIN 2/4to MAIN 3/4

SPEAKERS

DRIVER

WOOFER

IC801, 802: TAS5342LDDV

100 W stereo digital amplifier power stage

OTW 2

5

15

14

13

7

17

18

16

8

6

SD

M1

M2

M3

RESET_AB

RESET_CD

PWM_D

PWM_C

PWM_B

PWM_A

VDD

VREG

AGND

GND

OC_ADJ

GVDD_D

BST_D

PVDD_D

OUT_D

GND_D

GVDD_C

BST_C

PVDD_C

OUT_C

GND_C

GVDD_B

BST_B

PVDD_B

OUT_B

GND_B

GVDD_A

BST_A

PVDD_A

OUT_A

GND_A

Internal Pullup

Resistors to VREG

Protection

and

I/O Logic

Under-

voltage

Protection

Power

On

Reset

Te mp.

Sense

VREG

4

4

Isense

PWM

Rcv.

Ctrl.

Timing

PWM

Rcv.

Ctrl.

Timing

Gate

Drive

Gate

Drive

BTL/PBTL-Configuration

Pulldown Resistor

BTL/PBTL-Configuration

Pulldown Resistor

BTL/PBTL-Configuration

Pulldown Resistor

BTL/PBTL-Configuration

Pulldown Resistor

Ctrl.

Timing

Gate

Drive

Ctrl.

Timing

Gate

Drive

PWM

Rcv.

PWM

Rcv.

Overload

Protection

21

12

11

10

9

23

28

24

26, 27

29

22

33

32

31

30

1

36

34

35

37

44

39

43

40, 41

38

IC800: TAS5086DBT

PWM processor

DVDD

Power

Supply

Serial

Data

Interface

Channel

Selector

Block

Down-

mix

Clock Rate

/Error

Detection

and PLL

Serial

Control

Interface

System

Control

MUX

MUX MUX

6

DVSS

DVSS_ESD

VR_DIG

VR_ANA

VR_OSC

AVDD

AVSS_PLL

VREG_EN

SDIN1

SDIN2

SDIN3

SDIN4

MCLK

SCLK

LRCLK

PLLFLTP

PLLFLTM

HFCLK

OSCFLT

OSC_RES

SDA

SCL

RESET

PDN

MUTE

BKNDERR

SDIN4 1-5 1-5

1-6

L’

L’

1LF

MUX

MUX

PWM

Control

Channel Six Processing

Bass Management

R’

2RF

5C

(L’+R’)/2

MUX

I2S Serial

Output

Downmix

SDIN4

(L’+R’)/2

3LS

Ch

1-6

Vol PWM

4RS

R’

1-6

Chan.

PWM1

MUX

6

PWM2

MUX

6

PWM3

MUX

6

PWM4

MUX

6

PWM5

MUX

6

PWM6

VALID1

VALID2

SDOUT

VR_ANA 1

AVDD 2

AVSS 3

AVSS 4

PLL_FLTM 5

PLL_FLTP 6

AVSS 7

MCLK 8

RESET 9

PDN 10

DVDD 11

DVSS 12

DVSS_OSC 13

OSC_RES 14

VR_OSC 15

MUTE 16

SDA 17

SCL

LRCLK

PWM_1

PWM_2

PWM_3

PWM_4

PWM_5

PWM_6

VALID2

VALID1

VR_DIG

DVSS

DVSS

BKND_ERR

SDIN1

SDIN2

SDIN3

SDIN4

SDOUT

RESERVED

SCLK

18

19

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

to SUB_W206

Page 105

K7