Computer Hardware User's Manual

TMP92CM22

2007-02-16

92CM22-37

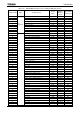

(4) Detailed description of the transfer mode register

0 0 0 Mode DMAM0 to DMAM7

DMAM [4:0] Operation Execution Time

000 zz

Destination address INC mode

(DMADn +) ← (DMASn)

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

5 states

001 zz

Source address DEC mode

(DMADn −) ← (DMASn)

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

5 states

010 zz

Source address INC mode

(DMADn) ← (DMASn +)

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

5 states

011 zz

Source address DEC mode

(DMADn) ← (DMASn −)

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

5 states

100 zz

Source address INC mode

(DMADn +) ← (DMASn +)

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

6 states

101 zz

Source address DEC mode

(DMADn −) ← (DMASn −)

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

6 states

110 zz

Destination address fixed mode

(DMADn) ← (DMASn)

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

5 states

111 00

Counter mode

DMASn ← DMASn + 1

DMACn ← DMACn − 1

If DMACn = 0 then INTTC

5 states

ZZ : 00 = 1-byte transfer

: 01 = 2-byte transfer

: 10 = 4-byte transfer

: 11 = (Reserved)

Note 1: The execution state number shows number of best case (1-state memory access).

1 state = 50 ns (at internal 20 MHz)

Note 2: “n” shows micro DMA channel number (0 to 7).