Datasheet

MSP430F23x

MSP430F24x(1)

MSP430F2410

www.ti.com

SLAS547I –JUNE 2007–REVISED DECEMBER 2012

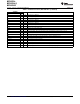

Memory Organization

Table 12. Memory Organization

MSP430F249

MSP430F233 MSP430F235

MSP430F2491

Memory Size 8KB 16KB 60KB

Main: interrupt vector Flash 0xFFFF to 0xFFC0 0xFFFF to 0xFFC0 0xFFFF to 0xFFC0

Main: code memory Flash 0xFFFF to 0xE000 0xFFFF to 0xC000 0xFFFF to 0x1100

RAM (Total) Size 1KB 2KB 2KB

0x05FF to 0x0200 0x09FF to 0x0200 0x09FF to 0x0200

Information memory Size 256 Byte 256 Byte 256 Byte

Flash 0x10FF to 0x1000 0x10FF to 0x1000 0x10FF to 0x1000

Boot memory Size 1KB 1KB 1KB

ROM 0x0FFF to 0x0C00 0x0FFF to 0x0C00 0x0FFF to 0x0C00

RAM Size 1KB 2KB 2KB

0x05FF to 0x0200 0x09FF to 0x0200 0x09FF to 0x0200

Peripherals 16 bit 0x01FF to 0x0100 0x01FF to 0x0100 0x01FF to 0x0100

8 bit 0x00FF to 0x0010 0x00FF to 0x0010 0x00FF to 0x0010

SFR 0x000F to 0x0000 0x000F to 0x0000 0x000F to 0x0000

MSP430F247 MSP430F248

MSP430F2410

MSP430F2471 MSP430F2481

Memory Size 32KB 48KB 56KB

Main: interrupt vector Flash 0xFFFF to 0xFFC0 0xFFFF to 0xFFC0 0xFFFF to 0xFFC0

Main: code memory Flash 0xFFFF to 0x8000 0xFFFF to 0x4000 0xFFFF to 0x2100

RAM (total) Size 4KB 4KB 4KB

0x20FF to 0x1100 0x20FF to 0x1100 0x20FF to 0x1100

Extended Size 2KB 2KB 2KB

0x20FF to 0x1900 0x20FF to 0x1900 0x20FF to 0x1900

Mirrored Size 2KB 2KB 2KB

0x18FF to 0x1100 0x18FF to 0x1100 0x18FF to 0x1100

Information memory Size 256 Byte 256 Byte 256 Byte

Flash 0x10FF to 0x1000 0x10FF to 0x1000 0x10FF to 0x1000

Boot memory Size 1KB 1KB 1KB

ROM 0x0FFF to 0x0C00 0x0FFF to 0x0C00 0x0FFF to 0x0C00

RAM (mirrored at Size 2KB 2KB 2KB

0x18FF to 0x1100) 0x09FF to 0x0200 0x09FF to 0x0200 0x09FF to 0x0200

Peripherals 16 bit 0x01FF to 0x0100 0x01FF to 0x0100 0x01FF to 0x0100

8 bit 0x00FF to 0x0010 0x00FF to 0x0010 0x00FF to 0x0010

SFR 0x000F to 0x0000 0x000F to 0x0000 0x000F to 0x0000

Bootstrap Loader (BSL)

The MSP430 bootstrap loader (BSL) enables users to program the flash memory or RAM using a UART serial

interface. Access to the MSP430 memory via the BSL is protected by user-defined password. For complete

description of the features of the BSL and its implementation, see the MSP430 Programming Via the Bootstrap

Loader User’s Guide (SLAU319).

Table 13. BSL Function Pins

BSL FUNCTION PM, RGC PACKAGE PINS

Data transmit 13 - P1.1

Data receive 22 - P2.2

Flash Memory

The flash memory can be programmed via the JTAG port, the bootstrap loader, or in-system by the CPU. The

CPU can perform single-byte and single-word writes to the flash memory. Features of the flash memory include:

• Flash memory has n segments of main memory and four segments of information memory (A to D) of

Copyright © 2007–2012, Texas Instruments Incorporated Submit Documentation Feedback 19