Datasheet

7

MR to TC t

PLH,

t

PHL

C

L

= 50pF 4.5 - - 55 - 69 - 83 ns

C

L

= 15pF 5 - 23 - - - - - ns

Output Transition Time t

THL

,t

TLH

C

L

= 50pF 4.5 - - 15 - 19 - 22 ns

Input Capacitance C

IN

C

L

= 50pF - - - 10 - 10 - 10 pF

CP Maximum Frequency f

MAX

C

L

= 15pF 5 - 25 - - - - - MHz

Power Dissipation Capacitance

(Notes 4, 5)

C

PD

-5-27-----pF

NOTES:

3. Noncascaded operation only. With cascaded counters clock-to-terminal count propagation delays, count enables (

PE or TE)-to-clock SET

UP TIMES, and count enables (PE or TE)-to-clock HOLD TIMES determine maximum clock frequency. For example, with these HC de-

vices:

4. C

PD

is used to determine the dynamic power consumption, per package.

5. P

D

= V

CC

2

f

i

+ C

L

V

CC

2

f

o

where f

i

= Input Frequency, C

L

= Output Load Capacitance, V

CC

= Supply Voltage, f

o

= Output Frequency.

Switching Specifications Input t

r

, t

f

= 6ns (Continued)

PARAMETER SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO

85

o

C

-55

o

C TO

125

o

C

UNITSMIN TYP MAX MIN MAX MIN MAX

C

P

f

MAX

1

CP-to-TC prop delay + TE-to-CP Setup Time + TE-to-CP Hold Time

------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

1

60 30 0++

-----------------------------

11MHz≈==

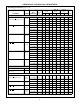

Timing Diagrams

FIGURE 1.

CP

MR

TE

PE

PL

P0

P1

P2

P3

P4

P5

P6

TC

P7

HC/HCT40103 COUNT

255 254 3 2 1 0 255 254 254 253 8 7 6 5 4 255 254 253 252

CD54HC40103, CD74HC40103, CD74HCT40103