Datasheet

7

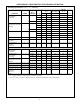

Test Circuits and Waveforms

FIGURE 2. HC TRANSITION TIMES AND PROPAGATION

DELAY TIMES, COMBINATION LOGIC

FIGURE 3. HCT TRANSITION TIMES AND PROPAGATION

DELAY TIMES, COMBINATION LOGIC

FIGURE 4. HC THREE-STATE PROPAGATION DELAY

WAVEFORM

FIGURE 5. HCT THREE-STATE PROPAGATION DELAY

WAVEFORM

NOTE: Open drain waveforms t

PLZ

and t

PZL

are the same as those for three-state shown on the left. The test circuit is Output R

L

=1kΩ to

V

CC

, C

L

= 50pF.

FIGURE 6. HC AND HCT THREE-STATE PROPAGATION DELAY TEST CIRCUIT

t

PHL

t

PLH

t

THL

t

TLH

90%

50%

10%

50%

10%

INVERTING

OUTPUT

INPUT

GND

V

CC

t

r

= 6ns t

f

= 6ns

90%

t

PHL

t

PLH

t

THL

t

TLH

2.7V

1.3V

0.3V

1.3V

10%

INVERTING

OUTPUT

INPUT

GND

3V

t

r

= 6ns

t

f

= 6ns

90%

50%

10%

90%

GN

D

V

CC

10%

90%

50%

50%

OUTPUT

DISABLE

OUTPUT LOW

TO OFF

O

UTPUT HIGH

TO OFF

OUTPUTS

ENABLED

OUTPUTS

DISABLED

OUTPUTS

ENABLED

6ns 6ns

t

PZH

t

PHZ

t

PZL

t

PLZ

0.3

2.7

GN

D

3V

10%

90%

1.3V

1.3V

OUTPUT

DISABLE

OUTPUT LOW

TO OFF

O

UTPUT HIGH

TO OFF

OUTPUTS

ENABLED

OUTPUTS

DISABLED

OUTPUTS

ENABLED

t

r

6ns

t

PZH

t

PHZ

t

PZL

t

PLZ

6ns t

f

1.3

IC WITH

THREE-

STATE

OUTPUT

OTHER

INPUTS

T

IED HIGH

OR LOW

OUTPUT

DISABLE

V

CC

FOR t

PLZ

AND t

PZL

GND FOR t

PHZ

AND t

PZ

H

OUTPUT

R

L

= 1kΩ

C

L

50pF

CD54/74HC367, CD54/74HCT367, CD54/74HC368, CD74HCT368